Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

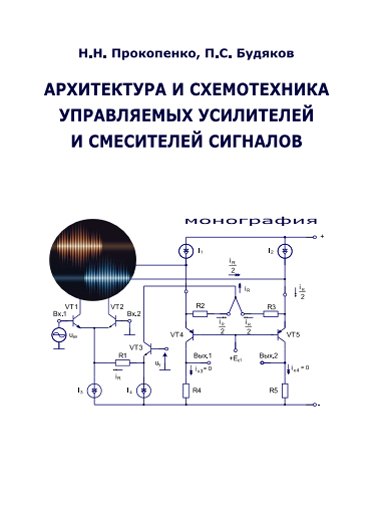

Архитектура и схемотехника управляемых усилителей и смесителей сигналов

Прокопенко Н Н, Будяков П С,

4.1. Аналоговый смеситель Гильберта с фазорасщепителем сигнала канала «Y» на основе токового зеркала

Существенный недостаток классического смесителя рис. 4.1 состоит

в том, что он имеет повышенные значения напряжения отрицательного

источника питания ( ), что не позволяет применять такую архитектуру в низковольтных IP-модулях и СФ-блоках c

), что не позволяет применять такую архитектуру в низковольтных IP-модулях и СФ-блоках c  .

.

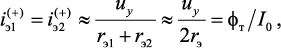

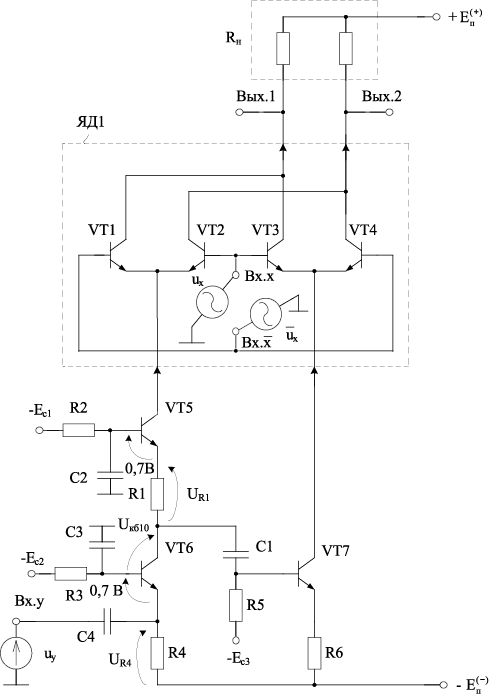

На рис. 4.1 представлена схема классического АСС, который содержит конкретное выполнение входной перемножающей ячейки Гильберта 1.

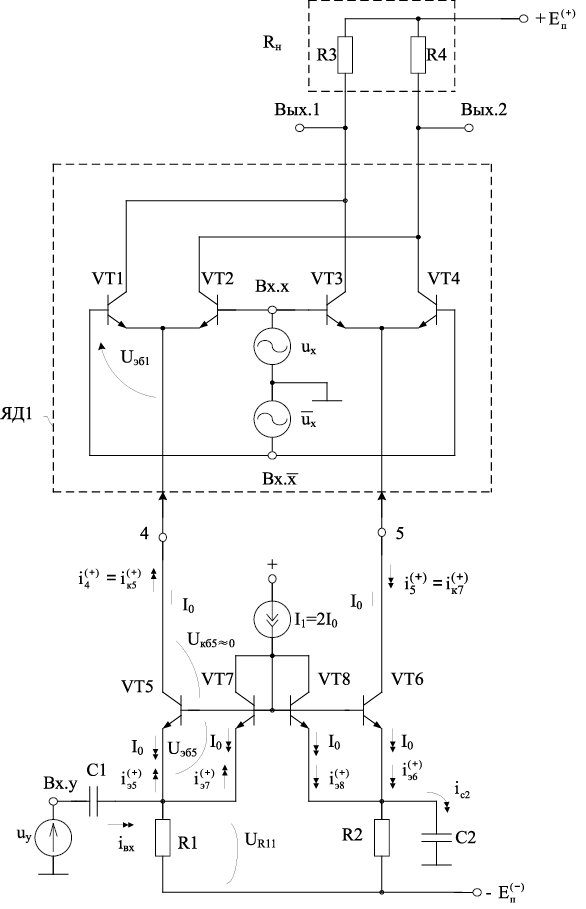

На рис. 4.2 представлена схема предлагаемого АСС. Решаемая им задача – уменьшение напряжения питания в сравнении с классической схемой не менее чем на один вольт при использовании однофазного сигнала по каналу «Y».

На рис. 4.2 перемножающая ячейка Гильберта (ЯД1) реализована по классической схеме на транзисторах VT1, VT2, VT3, VT4. Цепь нагрузки выполнена (в частном случае) на резисторах R3 и R4.

Синусоидальные напряжения первого смешиваемого сигнала ux (на входах Вх.х,  канала «Х» и второго смешиваемого сигнала uy (на входе Вх.y канала «Y»)

«перемножаются» традиционным образом в ячейке Гильберта.

канала «Х» и второго смешиваемого сигнала uy (на входе Вх.y канала «Y»)

«перемножаются» традиционным образом в ячейке Гильберта.

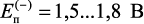

Переменное входное напряжение канала uy для диапазона частот, когда можно пренебречь сопротивлением разделительных конденсаторов C1 и C2, создаёт токи эмиттера транзисторов VT1 и VT2:

(4.1)

(4.1)

где rэ1 = rэ2 = rэ – сопротивления эмиттерных переходов транзисторов VT1 и VT2; φт = 26 мВ – температурный потенциал; 2I0 – статический ток токостабилизирующего двухполюсника I1.

Рис. 4.1. Схема классического АСС

Так как эмиттерно-базовые переходы транзисторов VT1 и VT5, а также

VT2 и VT6 включены параллельно, коллекторные токи транзисторов VT5

и VT6, и соответственно, входные токи ( ,

,  ) перемножающей ячейки Гильберта будут противофазны. Это является необходимым условием качественного смещения сигналов.

) перемножающей ячейки Гильберта будут противофазны. Это является необходимым условием качественного смещения сигналов.

Анализ рис. 4.4, а также 4.5, 4.6, 4.7 и 4.8 показывает, что предлагаемый смеситель обеспечивает достаточно качественное преобразование сигналов ux и uy.

Рис. 4.2. Схема предлагаемого АСС [32]

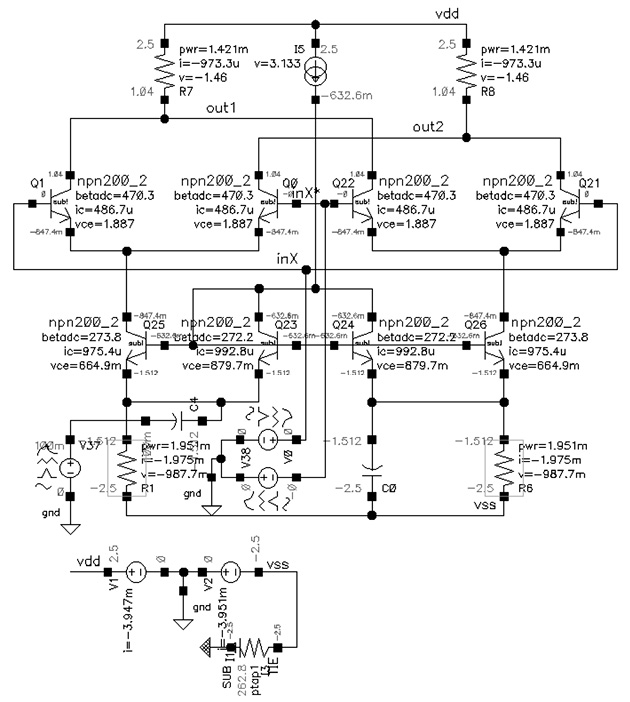

Рис. 4.3. Схема предлагаемого АСС в среде Cadence

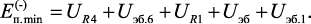

Для обеспечения работоспособности классического АСС минимально-возможное напряжение отрицательного источника питания  находится из уравнения Кирхгофа:

находится из уравнения Кирхгофа:

(4.2)

(4.2)

В предлагаемом СС:

(4.3)

(4.3)

Таким образом, в предлагаемом устройстве минимальное напряжение питания  отличается от напряжения питания классического АСС на величину:

отличается от напряжения питания классического АСС на величину:

(4.4)

(4.4)

В практических схемах с учетом реальных параметров элементов  , что весьма существенно для АСС с низковольтным питанием.

, что весьма существенно для АСС с низковольтным питанием.

На рис. 4.3 представлена схема предлагаемого смесителя в среде Cadence на моделях SiGe интегральных транзисторов.

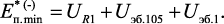

На рис. 4.4 приведена зависимость выходного дифференциального напряжения смесителя (рис. 4.3) от напряжения ux по каналу «X» при разных напряжениях Uy канала «Y».

Рис. 4.4. Зависимость выходного дифференциального напряжения смесителя от напряжения ux

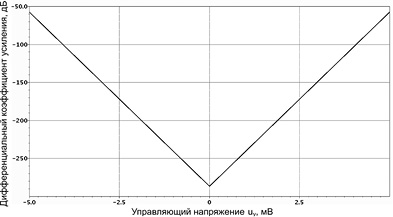

На рис. 4.5 показана зависимость модуля коэффициента усиления по напряжению Ку смесителя от напряжения управления uy по каналу «Y».

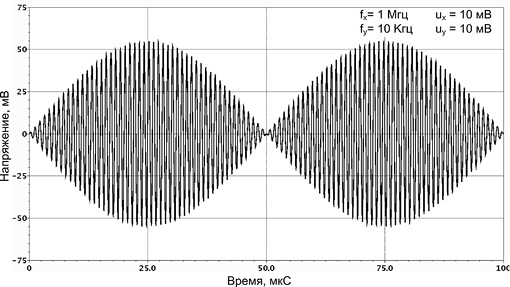

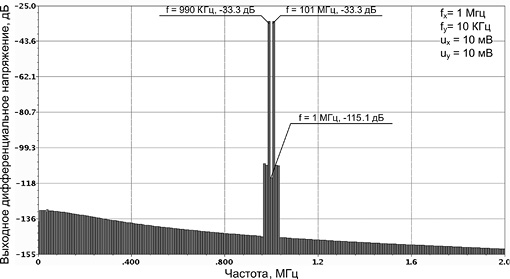

На рис. 4.6 представлена осциллограмма выходного сигнала смесителя (рис. 4.3), а на рис. 4.7 – спектр выходного сигнала смесителя-прототипа при fx = 1 МГц, fy = 10 КГц, ux = 10 мВ, uy = 10 мВ.

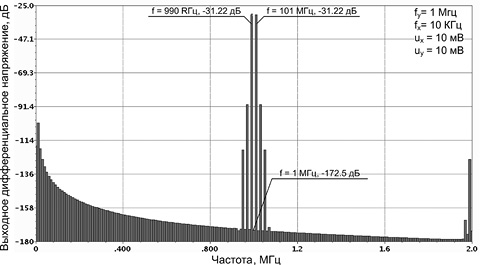

На чертеже рис. 4.8 показан спектр выходных сигналов предлагаемого АСС (рис. 4.3) при fy = 1МГц, fx = 10 КГц, ux = 10 мВ, uy = 10 мВ.

Таким образом, предлагаемый смеситель двух сигналов имеет существенные преимущества в сравнении с классическим, а также другими АСС с малым напряжением питания, использующим низкоомный однофазный вход по каналу «Y».

Рис. 4.5. Зависимость модуля коэффициента усиления по напряжению Ку смесителя от напряжения управления uy

Рис. 4.6. Осциллограмма выходного сигнала смесителя

Рис. 4.7. Спектр выходного сигнала классического смесителя

Рис. 4.8. Спектр выходных сигналов предлагаемого АСС