Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

Архитектура и схемотехника управляемых усилителей и смесителей сигналов

Прокопенко Н Н, Будяков П С,

13.4. Дополнительные модификации смесителей на основе токовых зеркал

Рассмотренная выше архитектура смесителя имеет несколько модификаций.

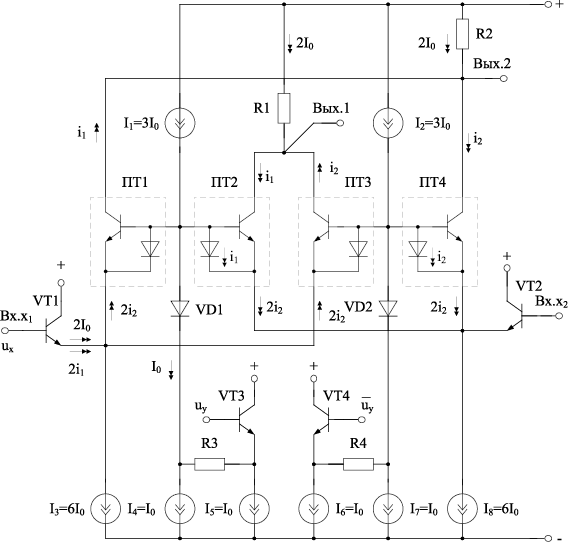

В схеме рис. 13.31 приняты дополнительные меры по повышению уровня входного сопротивления по каналу «Y».

Рис. 13.31. Архитектура смесителя

с повышенным входным сопротивлением по каналу «Y»

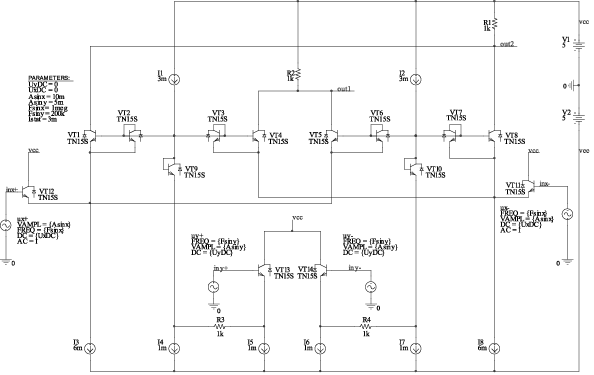

Компьютерная модель смесителя в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» приведена на рис. 13.32, а результаты моделирования на рис. 13.33–13.37.

Рис. 13.32. Модифицированный смеситель в среде PSpice на моделях транзисторов ФГУП НПП «Пульсар»

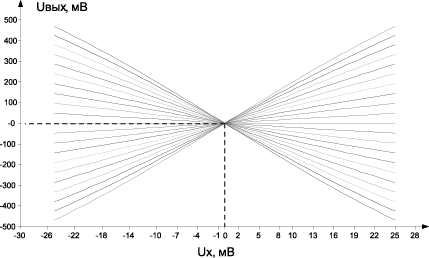

Проходная характеристика модифицированного смесителя в диапазоне низких частот приведена на рис. 13.33.

Рис. 13.33. Четырехквадрантная проходная характеристика смесителя

(входной сигнал Ux = Ux DC изменяется в диапазоне от –25 мВ до +25 мВ,

выход – дифференциальный)

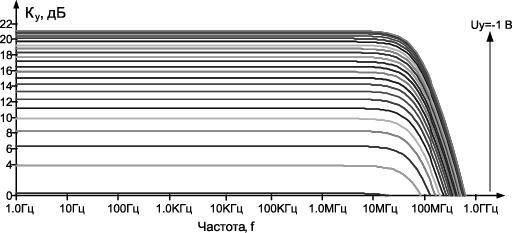

Рис. 13.34. Зависимость ЛАЧХ смесителя от управляющего напряжения Uy

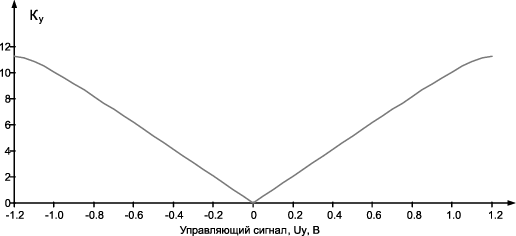

Рис. 13.35. Зависимость модуля Ку от управляющего напряжения Uy DC

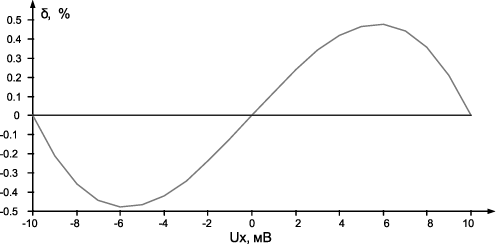

Погрешность перемножения двух малых сигналов не превышает 0,5 %, что достаточно для многих применений АПН (рис. 13.36).

Рис. 13.36. Относительная погрешность перемножения двух напряжений при входном сигнале Ux = –10 мВ...+10 мВ

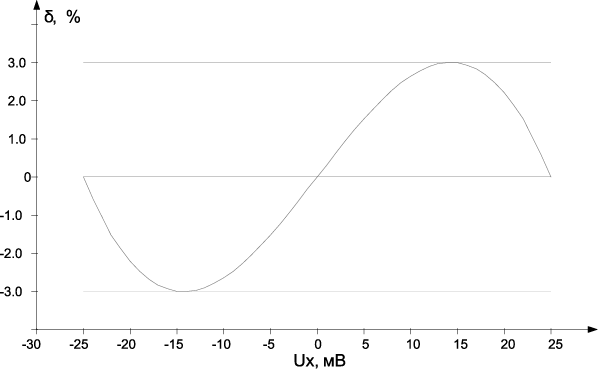

С увеличением Ux погрешность перемножения повышается (рис. 13.37).

Рис. 13.37. Погрешность перемножения при входном сигнале Ux = –25 мВ...+25 мВ

Для уменьшения ошибки δ в предлагаемом смесителе при изменении Uy в широком диапазоне сигналов целесообразно применить традиционное логарифмирование сигналов по Гильберту.