Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

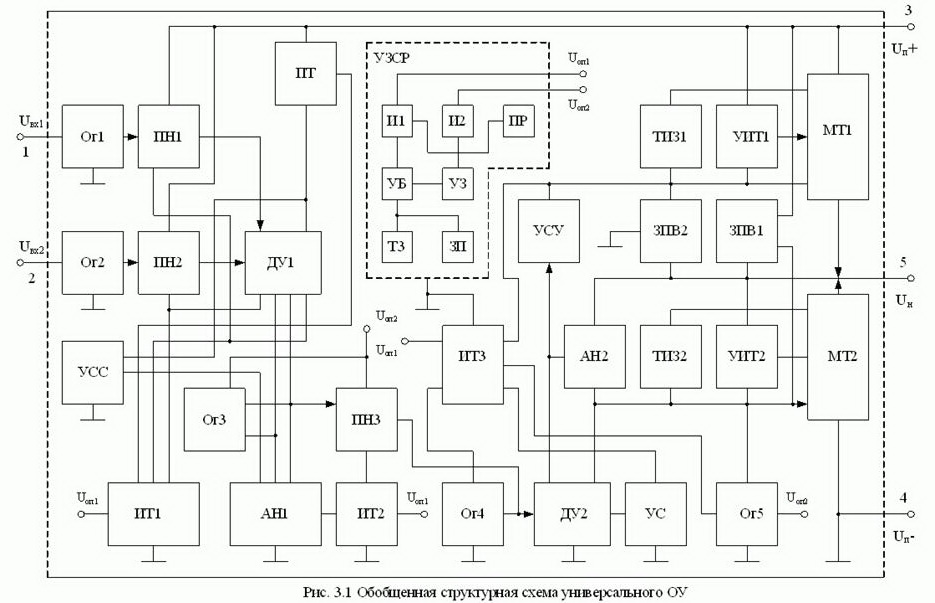

3.1 Обобщенная структурная схема универсального операционного усилителя (ОУ)

Во всех областях автоматического управления, контроля, измерительной техники, связи, бытовой электро- и радиоаппаратуре находят применение усилители мощности [84]. В результате достижений интегральной технологии, создания мощных, быстродействующих, сильноточных и высоковольтных транзисторов появились усилители мощности в виде единой микросхемы. Существующие в настоящее время интегральные усилители мощности отличаются большим разнообразием схемных и конструктивных решений, напряжений питания и токов нагрузки, в тоже время имеют крайне узкие функциональные возможности. Как правило, они не защищены от аварий в цепи нагрузки, питании, входных цепей и, как следствие, имеют ограниченную надежность [77].

Создание мощных интегральных операционных усилителей (МОУ), которые можно использовать в традиционных схемных решениях, построенных на основе интегральных операционных усилителей (ОУ), позволит решить существующие проблемы [82,85,87].

Развитие аналоговой микросхемотехники выдвигает проблему создания универсальных интегральных ОУ функционально интегрирующих в себе мощный и маломощный ОУ. Например, во многих изделиях, питаемых от аккумуляторных батарей (портативные компьютеры, автомобильная электроника и т.д.), усилители мощности с полной нагрузкой работают не постоянно. В этом случае повысить экономичность устройства в целом может усилитель, имеющий взаимосвязь между током нагрузки и током потребления.

Современные универсальные ОУ, как правило, строятся по двухаскадной структуре, позволяющей наиболее просто осуществить коррекцию ЛАЧХ и получить заданные эксплуатационные характеристики [32,41,42,52,72-81]. Первым каскадом (входным) обеспечиваются параметры ОУ со стороны входных клемм, вторым (выходным) - со стороны выходных клемм. Питание осуществляется от двухполярного источника.

Наряду с усилительными элементами, ОУ обычно включают в себя узлы, обеспечивающие режим по постоянному току микросхемы, а также узлы, выполняющие различные защитные и другие специальные функции (например, ограничение уровней сигналов, предотвращение режимов насыщения и отсечки элементов, работающих в активном режиме и т.д.).

Критерием схемотехнического совершенства современных изделий электронной техники является функциональная полнота, завершенность устройства в целом. В соответствии с этим предлагается обобщенная схема перестраиваемых универсальных ОУ, функционально интегрирующая в себе мощный и маломощный ОУ и позволяющая реализовать все эксплуатационные и защитные функции (рис.3-1).

Схема включает в себя: ограничители напряжения ОГ1-ОГ5; повторители напряжения ПН1-ПНЗ; повторитель тока ПТ; источники тока ИТ1-ИТЗ; дифференциальные усилители ДУ1, ДУ2; активные нагрузки дифференциальных усилителей АН1, АН2; узел смещения УС; узел сдвига уровня УСУ; мощные транзисторы МТ1,МТ2; управляемые источники тока УИТ1,УИТ2; узлы тепловой импульсной защиты ТИ31,ТИ32; узлы защиты от превышения выходного напряжения ЗПВ1, ЗПВ2; узел слежения за синфазным напряжением УСС; узел задания статического режима УЗСР, включающий в себя узлы тепловой защиты ТЗ и защиты от перенапряжения ЗП, узел блокировки УБ, узел запуска УЗ, переключатель режимов ПР, источники напряжения Иоп1 , Иоп2 . Микросхема имеет минимальное число (пять) выводов для подключения: входных напряжений - 1, 2; напряжений питания - 3, 4; нагрузки - 5.

.

.

Схема (рис.3.1) работает следующим образом. Входной сигнал подается на выводы 1 и 2, далее через элементы ОГ1 и ОГ2, ПН1 и ПН2 поступает на входы ДУ1, где он преобразуется из дифференциального в несимметричный.

Усиленный сигнал снимается с элемента АН1 и через ПНЗ подается на вход ДУ2, на другой вход которого подается напряжение смещения от элемента УС. Усиленный в ДУ2 сигнал снимается с АН2 и подается в противофазе на МТ2 и через элемент УСУ на МТ1. Сигналы, усиленные в элементах МТ1 и МТ2, поступают в нагрузку (путь прохождения сигнала показан на рис.3.1 стрелками).

Элементы ОГ1 и ОГ2 необходимы для ограничения входного сигнала на уровне не ниже потенциала ![]() . Элемент ИТ1 служит для питания элементов ПН1 и ПН2, а посредством ПТ питает ДУ1. Режим динамической перегрузки ДУ1 предотвращают ПН1 и ПН2. В случае увеличения входного сигнала выше допустимого уровня сигналы управления от ДУ1 поступают в цепи питания ПН1 и ПН2, уменьшая их коэффициент передачи и, таким образом, предотвращая перегрузку ДУ1 по входу. Элемент УСС позволяет элементам узла ДУ1 работать при неизменном напряжении питания, уменьшая коэффициент передачи синфазного сигнала. Элемент ОГЗ предназначен для двустороннего ограничения размаха напряжения на АН1 с целью исключения его насыщения. Элемент ОГ4 ограничивает уровень напряжения на входе ДУ2, предотвращая режим динамической перегрузки. Комплексную защиту от перегрузки МТ1 и МТ2 по току, температуре и мощности осуществляют ТИ31 и ТИ32 соответственно. Датчики температуры этих элементов расположены внутри мощных транзисторов. Для повышения эквивалентного коэффициента передачи по постоянному току МТ1 и МТ2 служат элементы УИТ1 и УИТ2 соответственно. Ток на выходе этих элементов пропорционален току на входе мощных транзисторов. Исключение переходных искажений достигается использованием элементов УСУ и ОГ5, которые предотвращают нахождение элементов МТ1 и МТ2 в режиме отсечки тока.

. Элемент ИТ1 служит для питания элементов ПН1 и ПН2, а посредством ПТ питает ДУ1. Режим динамической перегрузки ДУ1 предотвращают ПН1 и ПН2. В случае увеличения входного сигнала выше допустимого уровня сигналы управления от ДУ1 поступают в цепи питания ПН1 и ПН2, уменьшая их коэффициент передачи и, таким образом, предотвращая перегрузку ДУ1 по входу. Элемент УСС позволяет элементам узла ДУ1 работать при неизменном напряжении питания, уменьшая коэффициент передачи синфазного сигнала. Элемент ОГЗ предназначен для двустороннего ограничения размаха напряжения на АН1 с целью исключения его насыщения. Элемент ОГ4 ограничивает уровень напряжения на входе ДУ2, предотвращая режим динамической перегрузки. Комплексную защиту от перегрузки МТ1 и МТ2 по току, температуре и мощности осуществляют ТИ31 и ТИ32 соответственно. Датчики температуры этих элементов расположены внутри мощных транзисторов. Для повышения эквивалентного коэффициента передачи по постоянному току МТ1 и МТ2 служат элементы УИТ1 и УИТ2 соответственно. Ток на выходе этих элементов пропорционален току на входе мощных транзисторов. Исключение переходных искажений достигается использованием элементов УСУ и ОГ5, которые предотвращают нахождение элементов МТ1 и МТ2 в режиме отсечки тока.

Элементы Иоп1 и Иоп2„ служат для получения стабилизированных напряжений Uоп1 и Uоп2 соответственно, необходимых для задания статического режима. Элемент ПР осуществляет переключение режимов потребления тока МОУ в зависимости от тока нагрузки. При перегреве микросхемы срабатывает элемент ТЗ, который посредством УВ снижает величину напряжения Uоп1 до нуля и прекращает дальнейшее функционирование МОУ. Аналогично микросхема отключается и при срабатывании элемента ЗП, запрещающего работу МОУ при превышении напряжения питания микросхемы предельной величины. Элементы ЗПВ1 и ЗПВ2 ограничивают величину максимального напряжения на выходе на уровне, не превышающем напряжение питания положительной и отрицательной полярности. При этом блокируется протекание тока через МТ2 и МТ1 соответственно.

Таким образом, предлагаемая обобщенная структурная схема универсального ОУ позволяет реализовать устройство, отличающееся низким токопотреблением, высокой надежностью и эксплуатационными параметрами. Большой набор функциональных узлов в данной схеме обусловлен широким спектром реализуемых функций и совершенно не обязательно сопровождается элементной избыточностью, поскольку на этапе схемотехнического проектирования могут широко использоваться методы схемотехнической интеграции функциональных узлов. В случае снижения числа функций у проектируемого устройства отдельные элементы структурной схемы могут быть исключены.

В предлагаемой схеме (рис.3.1) за счет использования ключевых элементов в ПР реализован режим переключения статического режима ОУ в зависимости от уровня тока нагрузки Iн. При этом, чем меньше ток нагрузки Iн , тем меньше ток ![]() , потребляемый соответственно элементами ОУ (

, потребляемый соответственно элементами ОУ (![]() , где Iист - ток источника питания). При использовании N переключений зависимость

, где Iист - ток источника питания). При использовании N переключений зависимость ![]() имеет вид, представленный на рис.3.2,б [86].

имеет вид, представленный на рис.3.2,б [86].

Введем в рассмотрение важный энергетический параметр универсальных ОУ - коэффициент использования по току потребления Кп=Iн /Iист . При использовании режима переключения удается поддерживать коэффициент Kп. близким к единице в диапазоне как больших, так и малых токов нагрузки. Это особенно важно в тех случаях, когда большой ток нагрузки имеет кратковременный характер. При малых токах нагрузки и отсутствии режима переключения коэффициент Кп может быть очень мал (Кп=0,1-0,01).

Схема, представленная на рис. 3.2,а, реализует зависимость ![]() (рис.3-2,6). Она включает в себя датчики вытекающего и втекающего токов нагрузки ДТ1 и ДТ2; распределитель токов РТ; переключаемый источник тока ПИТ; N переключателей (П), каждый из которых состоит из устройства сравнения УС, источника опорного тока ИОТ, пикового детектора ПД, формирователя гистерезиса ФГ и ключа Кл.

(рис.3-2,6). Она включает в себя датчики вытекающего и втекающего токов нагрузки ДТ1 и ДТ2; распределитель токов РТ; переключаемый источник тока ПИТ; N переключателей (П), каждый из которых состоит из устройства сравнения УС, источника опорного тока ИОТ, пикового детектора ПД, формирователя гистерезиса ФГ и ключа Кл.

Вытекающий или втекающий через шины питания ОУ ток нагрузки Iн регистрируется элементами ДТ1 или ДТ2, токи на выходе которых пропорциональны току нагрузки. Распределитель токов суммирует токи Iд1, Iд2 и подает результирующий ток на каждый из элементов П, причем величина тока на выходе РТ равна Ii=Iд1+Iд1. При превышении входным сигналом i-го порога (Ii), различного для каждого элемента Пi происходит переключение элемента ПИТ из одного устойчивого состояния в другое. Величина тока Iп.i, на выходе ПИТ при его переключении определяет зависимость ![]() .

.

Каждый из элементов Пi, работает следующим образом. Элемент УС сравнивает входной сигнал Ii - с опорным I оп.i , в случае его превышения на выходе УС появляется сигнал высокого уровня, подаваемый через ПД на ключ. Для исключения колебательности в момент переключения служит ФГ, образующий гистерезисную характеристику передачи (рис.3.2.в). На этой характеристике значение ![]() соответствует току нагрузки, при котором ОУ переходит из режима с низким токопотреблением

соответствует току нагрузки, при котором ОУ переходит из режима с низким токопотреблением ![]() . к режиму с более высоким значением тока

. к режиму с более высоким значением тока ![]() . Значение

. Значение ![]() соответствует обратному переключению.

соответствует обратному переключению.

.

.

Для исключения искажений в момент перехода выходного тока через нулевое значение служит элемент ПД, задерживающий переключение Пi на время tЗ, достаточное для преодоления током нагрузки интервала ![]() .

.

Схемотехническая реализация структурной схемы ПР (рис.3.2.а) для двуступенчатого режима переключений, представлена на рис.3.3. Данная схема состоит из датчиков тока (ДТ1, ДТ2) VT18, R7 и VT20, R8; распределителя токов (РТ) VT15,VТ16 ограничителя (ОГ) VT17; пикового детектора (ПД) VT12, C1; ключа (КЛ) YT9-VT11, R4; источника опорных токов и напряжений (ИОТ) VT3-VT8, VT13, VT14; цепи запуска (ЦЗ) VT1, VT2, R1. В разработанной схеме пиковый детектор схемотехнически интегрирован с устройством сравнения и формирователем гистерезиса. Источник опорных токов и напряжения является общим для всего переключателя режимов и в случае многозонной характеристики переключения (рис.3.2.б) может быть использован для задания статических режимов оставшихся элементов.

Максимальный потенциал базы транзистора VT12 ограничен напряжением пробоя обратносмещенного эмиттерного перехода транзистора VT17 (Uог). Заряд емкости С1 вызывает рост потенциала базы транзистора VT11. Когда потенциалы баз транзисторов VT10 и VT11 сравниваются, открывается транзистор VT9, и происходит переключение элемента ПИТ (рис.3.2.а) сигналом U1 из одного устойчивого состояния в другое. Обратное переключение происходит, когда ток Iк14 становится меньше тока Iк15, на величину тока Iк13. Тем самым формируется гистерезисная характеристика передачи ![]() (рис.3.2.б). Транзистор VT12 закрывается, конденсатор С1 разряжается током коллектора транзистора VT13. Время задержки переключения определяется выражениями:

(рис.3.2.б). Транзистор VT12 закрывается, конденсатор С1 разряжается током коллектора транзистора VT13. Время задержки переключения определяется выражениями:

![]() , (3.1)

, (3.1)

, (3.2)

, (3.2)

где Uбэi, Si - напряжение и площадь перехода база-эмиттер i-го транзистора. Для получения температурно независимой величины задержки времени tз ток I0 выбирается с заданным положительным температурным дрейфом.

Значения токов переключения ![]() и

и ![]() определяются соотношениями:

определяются соотношениями:

для вытекающего тока нагрузки

![]() , (3.3)

, (3.3)

для втекающего тока нагрузки

![]() , (3.4)

, (3.4)

![]() . (3.5)

. (3.5)

Таким образом, предлагаемое схемотехническое решение позволяет реализовать переключатель режимов для двуступенчатого регулирования тока потребления универсального ОУ, обладает минимальной задержкой включения и температурно независимым временем выключения.

Рассмотрим методы построения многоканальных ПИТ, для использования их в узлах задания статического режима универсального ОУ. К таким ПИТ предъявляются следующие требования:

- возможность переключения выходных токов одновременно во всех каналах;

- возможность получения выходных токов, как с положительным, так и с отрицательным температурным коэффициентом;

- часть выходных токов должна быть втекающими, а часть вытекающими;

- возможность увеличения числа выходных токов.

Схема многоканального ПИТ (рис. 3-4) наиболее полно выполняет все перечисленные требования. Она состоит из цепи запуска R1, VT1, VТ2;

формирователя опорных токов R2, R3, VT5, VT6, VT9- VТ12; токового зеркала R4, VT3, VT4, VT7, VT8.

Опорный ток I оп многоканального ПИТ и выходные токи I 1 , I 2 , I 3, I 4 определяются следующими соотношениями:

, (3.5)

, (3.5)

, (3.6)

, (3.6)

, (3.7)

, (3.7)

где  ,

,

,

,

Sкi, Sэi - площади коллекторных и эмиттерных переходов i-тых транзисторов. Из соотношений (3-5)-(3.5) видно, что токи I3, I4 имеют отрицательный температурный коэффициент, ток I2 - положительный температурный коэффициент. Анализ показывает, что для получения положительного температурного дрейфа тока I1 необходимо выполнение следующего условия:

, (3.8)

, (3.8)

где Тмакс - максимальная рабочая температура ОУ.

Наращивание количества выходных токов такого ПИТ осуществляется путем подключения дополнительных транзисторов к потенциалам Uсм1-Uсм2.

Переключение режима данного ПИТ осуществляется коммутацией дополнительных резисторов , шунтирующих основной токозадающий резистор R2 . К выводу U1 подключается выход устройства переключения режимов (рис. 3.3).

Таким образом, предлагаемая обобщенная структурная схема перестраиваемого мощного ОУ, способы построения переключателя режимов и переключаемого источника тока позволяют синтезировать универсальный ОУ, обладающий улучшенными энергетическими характеристиками.