Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

Архитектура и схемотехника управляемых усилителей и смесителей сигналов

Прокопенко Н Н, Будяков П С,

4.2. Комплементарный аналоговый смеситель сигналов с однофазным управлением по каналу «Y»

Аналоговый смеситель сигналов (АСС) является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов.

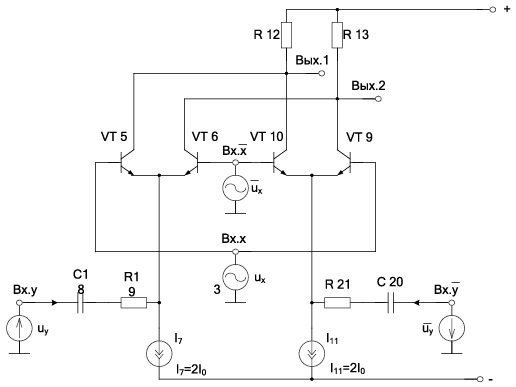

Прототипом заявляемого устройства, архитектура которого присутствует также и в других АСС [33, 34], является аналоговый смеситель сигналов рис. 4.9.

Рис. 4.9. Схема АСС-прототипа

Существенный недостаток известного смесителя состоит в том, что для обеспечения его работоспособности необходимо иметь два противофазных сигнала по каналу «Y», что требует применения специальных фазорасщепителей – так называемых «балунов» (balun). В конечном итоге введение фазорасщепителей и их фазовая погрешность отрицательно сказываются на качестве смешения (перемножения) двух сигналов канала «X» и канала «Y».

Основная задача предполагаемого изобретения состоит в обеспечении работоспособности смесителя сигналов при однофазном управлении по каналу «Y».

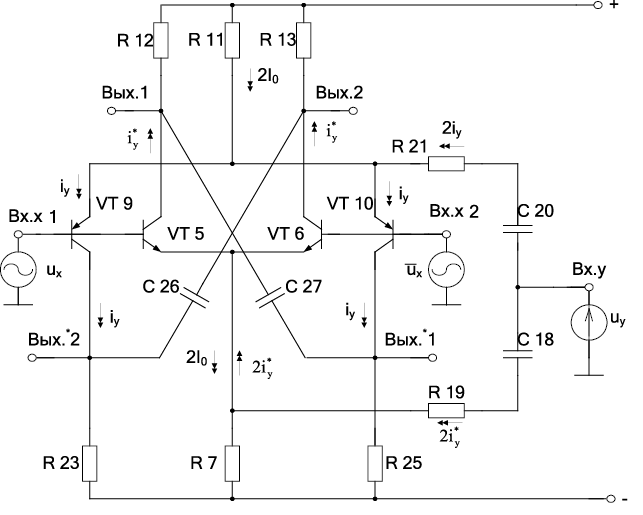

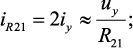

Рассмотрим работу АСС рис. 4.10 в диапазоне средних частот, когда влиянием конденсаторов C18, C20 и C26, C27 можно пренебречь из-за малого сопротивления на переменном токе [35].

Рис. 4.10. Схема модифицированного АСС [35]

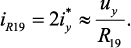

Увеличение напряжения uy канала «Y» (положительная «полуволна») приводит к появлению синфазных токов через резисторы R21 и R19, которые «втекают» в общие эмиттерные цепи транзисторов VT9, VT10 и VT5, VT6:

(4.5)

(4.5)

(4.6)

(4.6)

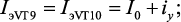

При этом токи эмиттеров транзисторов VT9 и VT10 увеличиваются от

статического уровня I0 на величину iy, а токи эмиттеров транзисторов VT5

и VT6 уменьшаются на величину  от статического уровня I0:

от статического уровня I0:

(4.7)

(4.7)

(4.8)

(4.8)

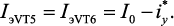

При увеличении суммарного тока эмиттерной цепи транзисторов VT9 и VT10 их коэффициент усиления по напряжению со входов Вх.х1 и Вх.х2 увеличивается

(4.9)

(4.9)

а транзисторов VT5 и VT6 уменьшается

(4.10)

(4.10)

где φ ≈ 26 мВ – температурный потенциал; Rн.экв – эквивалентное сопротивление нагрузки в цепи выходов Вых. 16, Вых. 22 и Вых. 15, Вых. 24.

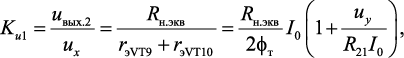

Поэтому, дифференциальное выходное напряжение АСС между выходами Вых. 15 и Вых. 16 пропорционально произведению ux и uy:

(4.11)

(4.11)

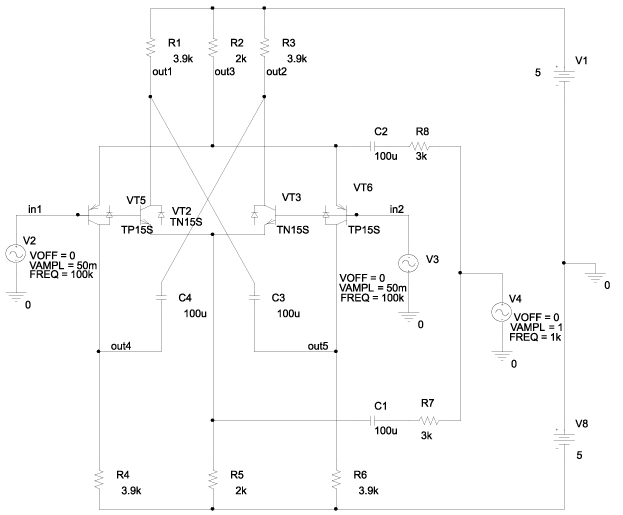

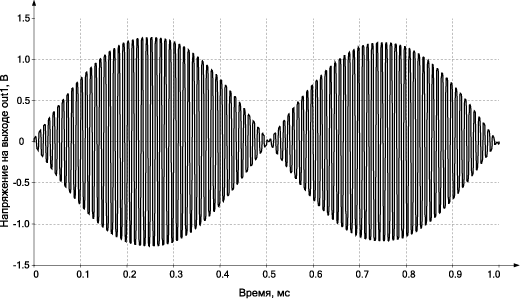

Из формулы (4.11) следует, что заявляемое устройство обеспечивает смешение (перемножение) двух сигналов при однофазном управлении по каналу «Y», что подтверждается результатами моделирования рис. 4.12, рис. 4.13. На чертеже рис. 4.11 представлена схема заявляемого АСС в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Рис. 4.11. Схема АСС в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар»

Рис. 4.12. Осциллограмма выходного напряжения АСС,

при Ux = 150 мВ, fx = 100 КГц, Uy = 1 В, fy = 1 KГц

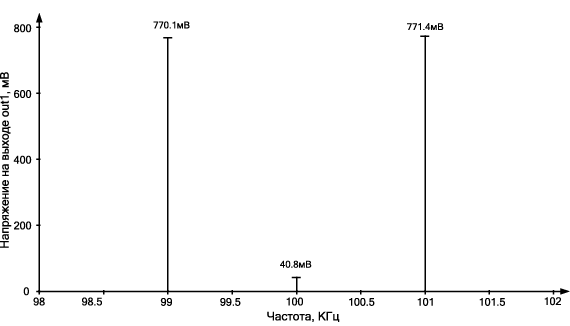

Рис. 4.13. Спектр выходного сигнала АСС,

при Ux = 150 мВ, fx = 100 КГц, Uy = 1 В, fy = 1 KГц

В СВЧ смесителях сигналов рис. 4.10 резисторы R21 и R19 могут выполнять функции устройств согласования источника входного напряжения канала «Y» 17 uy и АСС с заданным волновым сопротивлением, например, 50 Ом.

Особенность схемы рис. 4.10 – возможность работы при малых напряжениях питания (например, ±1 В), что позволяет рекомендовать его схему для использования в системах СВЧ-связи, реализуемых на основе SiGe техпроцессов.

Таким образом, схема рис. 4.10 является дальнейшим развитием широко распространенного смесителя Гильберта и характеризуется отсутствием фазорасщепителя сигнала по каналу «Y» – одного из основных источников погрешности АСС.