Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

Архитектура и схемотехника управляемых усилителей и смесителей сигналов

Прокопенко Н Н, Будяков П С,

6.3. Аналоговый смеситель сигналов на базе дифференциального каскада Дарлингтона

Управляемый усилитель и смеситель аналоговых сигналов на базе дифференциального каскада Дарлингтона может быть использован в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого со входов канала «Х» зависит от уровня сигнала управления канала «Y». Управляемый усилитель и аналоговый смеситель сигналов (УУ) являются базовыми узлами систем приема и обработки сигналов ВЧ и СВЧ-диапазонов.

В современной микроэлектронике широкое применение получили дифференциальные каскады (ДК) на составных транзисторах. Их коэффициент усиления по напряжению зависит от величины статического тока общей эмиттерной цепи ДК (Iy = I0) и, следовательно, такие ДК являются (при электронном изменении величины тока Iy = I0) управляемыми усилителями (УУ).

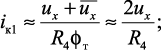

Существенный недостаток классического УУ рис. 6.23 состоит в том, что при электронном управлении величиной коэффициента усиления (Ky) фаза выходного напряжения в рабочем диапазоне частот дифференциального каскада (ДК) не изменяется на 180°. Как следствие, это не позволяет использовать известный ДК в структуре ряда устройств радиотехники, например, в качестве смесителя аналоговых сигналов, фазовых детекторов и т.п.

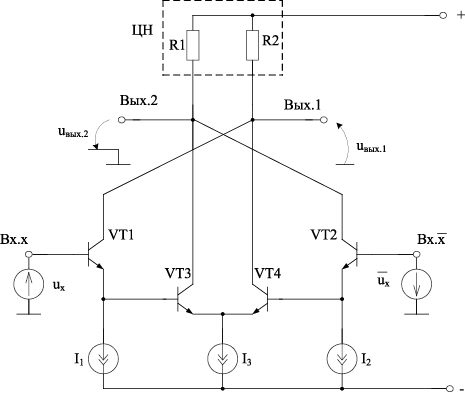

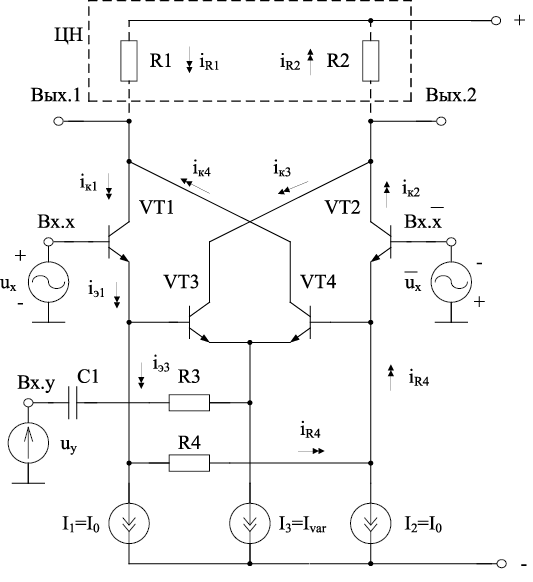

На рис. 6.24 показана схема предлагаемого управляемого усилителя и смесителя аналоговых сигналов на базе дифференциального каскада Дарлингтона. Его задача – получение на выходе ДК не только амплитудных изменений выходного сигнала под действием управляющего напряжения канала «Y», но и его фазы. Как следствие, это позволяет создавать на основе предлагаемого устройства смесители аналоговых сигналов с хорошим подавлением основной гармоники.

Рассмотрим работу УУ рис. 6.24 в диапазоне частот, когда влиянием конденсатора С1 можно пренебречь из-за его малого сопротивления на переменном токе в сравнении с сопротивлением резистора R3.

Рис. 6.23. Схема классического УУ [46]

Входной сигнал (ux и  )

канала «Х» передается от источников напряжений в цепь нагрузки ЦН на

выходы (Вых. 1 и Вых. 2) по двум каналам. Первый инвертирующий (для

выхода Вых. 1 (Вых. 2)) канал, образуемый каскадом с общим эмиттером на

транзисторе VT1 (VT2), инвертирует фазу сигнала ux (

)

канала «Х» передается от источников напряжений в цепь нагрузки ЦН на

выходы (Вых. 1 и Вых. 2) по двум каналам. Первый инвертирующий (для

выхода Вых. 1 (Вых. 2)) канал, образуемый каскадом с общим эмиттером на

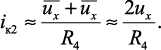

транзисторе VT1 (VT2), инвертирует фазу сигнала ux ( ) к соответствующему выходу Вых. 1 (Вых. 2). При этом крутизна преобразования ux и

) к соответствующему выходу Вых. 1 (Вых. 2). При этом крутизна преобразования ux и  в приращения коллекторных токов транзисторов VT1 и VT2 определяется сопротивлением резистора R4

в приращения коллекторных токов транзисторов VT1 и VT2 определяется сопротивлением резистора R4

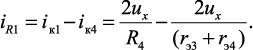

(6.20)

(6.20)

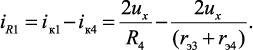

(6.21)

(6.21)

Второй канал передачи сигналов канала «Х» к выходу Вых. 1 (Вых. 2) – неинвертирующий. Он связан с наличием напряжений ux и  на базах транзисторов VT3 и VT4 и их преобразованием в коллекторные

токи транзисторов VT3 и VT4. Коэффициенты преобразования напряжений ux

и

на базах транзисторов VT3 и VT4 и их преобразованием в коллекторные

токи транзисторов VT3 и VT4. Коэффициенты преобразования напряжений ux

и  в выходные токи этого канала зависят от уровня тока iΣ(t) в общей эмиттерной цепи транзисторов VT3 и VT4

в выходные токи этого канала зависят от уровня тока iΣ(t) в общей эмиттерной цепи транзисторов VT3 и VT4

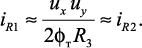

(6.22)

(6.22)

(6.23)

(6.23)

где rэ3, rэ4 – сопротивления эмиттерных переходов соответствующих транзисторов VT3 и VT4

Рис. 6.24. Схема предлагаемого УУ [47]

(6.24)

(6.24)

причем суммарный ток общей эмиттерной цепи транзисторов VT3 и VT4 iΣ(t) зависит от управляющего напряжения uy:

(6.25)

(6.25)

Как следствие, суммарный ток в резисторе R1 дифференциальной цепи нагрузки ЦН имеет две разностные составляющие

(6.26)

(6.26)

Таким образом, в резисторе нагрузки R1 протекают две противофазные составляющие токов, обусловленные входным сигналом ux канала «Х» и напряжения uy канала «Y»:

(6.27)

(6.27)

Схема рис. 6.24 настраивается таким образом, чтобы при uy = 0 переменный ток в резисторе R1 (R2) был равен нулю, что обеспечивается соответствующим выбором резистора R4 и тока I3

(6.28)

(6.28)

Если суммарный ток общей эмиттерной цепи транзисторов VT3 и VT4

под действием источника управляющего напряжения (uy) становится меньше

или больше, чем статический ток I3, то происходит изменение фазы

выходного сигнала ДК – в схеме преобладает либо первый инвертирующий

канал передачи ux и  через транзисторы VT1 и VT2, либо второй неинвертирующий канал

(транзисторы VT3, VT4). Этот эффект достигается за счет новых связей

в предлагаемом ДК и является необходимым условием для реализации на его

основе не только управляемого фазочувствительного (к управляющему

сигналу канала «Y») усилителя, но и смесителя сигналов ux и uy каналов

«Х» и «Y».

через транзисторы VT1 и VT2, либо второй неинвертирующий канал

(транзисторы VT3, VT4). Этот эффект достигается за счет новых связей

в предлагаемом ДК и является необходимым условием для реализации на его

основе не только управляемого фазочувствительного (к управляющему

сигналу канала «Y») усилителя, но и смесителя сигналов ux и uy каналов

«Х» и «Y».

Таким образом, переменные токи в резисторах R1 и R2

(6.29)

(6.29)

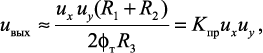

Поэтому переменная составляющая выходного дифференциального напряжения УУ рис. 6.24 является произведением напряжений ux и uy:

(6.30)

(6.30)

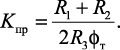

где  .

.

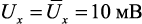

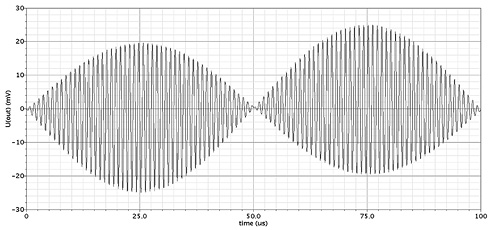

Из (11) следует, что предлагаемое устройство обеспечивает смешение (перемножение) двух сигналов ux и uy, что подтверждается результатами моделирования (рис. 6.29, рис. 6.30).

В СВЧ смесителях сигналов рис. 6.24 резистор R3 может выполнять функцию цепи согласования источника входного напряжения канала «Y» с заданным волновым сопротивлением, например, 100 Ом.

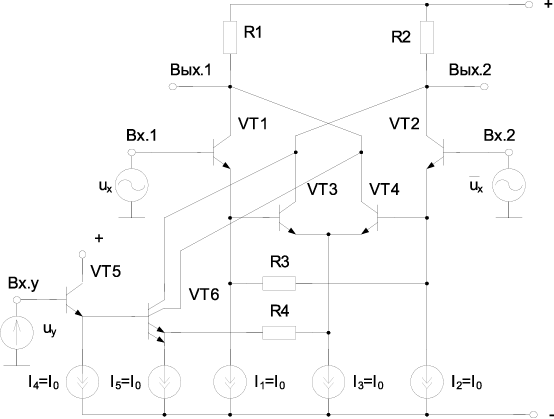

На рис. 6.25 показан пример применения предлагаемого УУ для случая, когда источник управляющего напряжения канала «Y» связан с объединёнными эмиттерами входных транзисторов VT3, VT4 через повторитель напряжения на транзисторах VT5, VT6 и резистор R4. Данное схемотехническое решение иллюстрирует другие модификации предлагаемого устройства. В частности, выполнение транзистора VT6 в схеме рис. 6.25 на основе сдвоенного биполярного транзистора и подключение соответствующих коллекторов сдвоенного биполярного транзистора VT6 к выходам устройства способствует дальнейшему повышению уровня подавления основной гармоники смесителя рис. 6.25. Статический режим транзисторов VT5 и VT6 в схеме рис. 6.25 устанавливается источниками опорного тока I3 и I4. В частном случае, коллекторы сдвоенных транзисторов VT6 могут соединяться с положительным источником питания.

Рис. 6.25. Схема предлагаемого УУ с повышенным

уровнем подавления основной гармоники

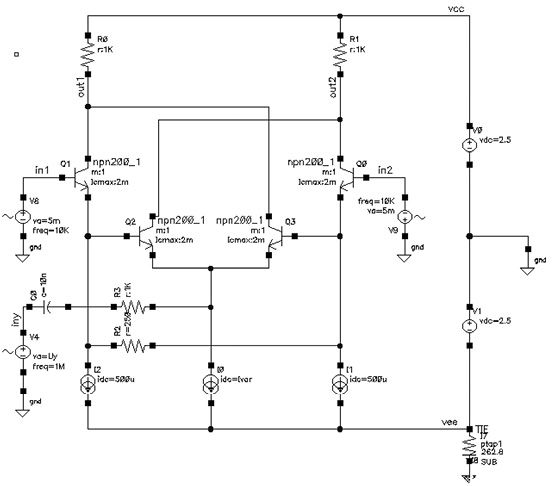

На рис. 6.26 представлена схема предлагаемого УУ рис. 6.24 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Рис. 6.26. Схема предлагаемого УУ рис. 6.24 в среде PSpice

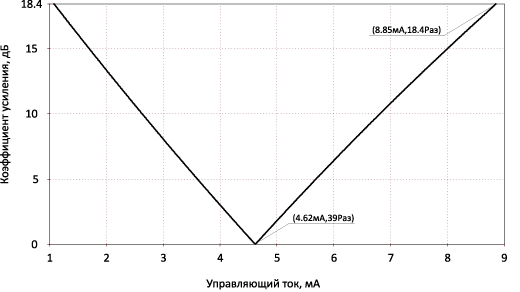

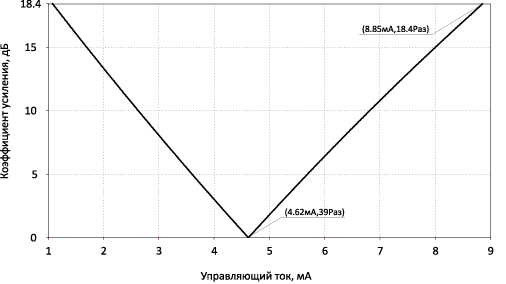

На рис. 6.27 показана зависимость модуля коэффициента усиления по напряжению от величины статического тока I3 токостабилизирующего двухполюсника схемы рис. 6.26. Данный график, а также анализ показывают, что при токе I3 < 4,6 мА выходной сигнал УУ имеет фазу, противоположную фазе входного напряжения ux = V6, а при I3 > 4,6 мА выходной сигнал УУ имеет фазу, совпадающую с фазой входного напряжения ux = V6.

Рис. 6.27. Зависимость модуля коэффициента усиления

по напряжению от величины статического тока

На рис. 6.28 представлена схема предлагаемого УУ рис. 6.24 в среде Cadence на моделях SiGe интегральных транзисторов.

Рис. 6.28. Схема предлагаемого УУ рис. 6.24 в среде Cadence

На рис. 6.29 показана осциллограмма выходного сигнала схемы УУ

рис. 6.28 при напряжениях источников противофазных входных напряжений

(канал «Х»)  и частоте Fx = 10 кГц, а также при напряжении источника управляющего сигнала (канал «Y») Uy = 200 мВ с частотой Fy = 1 МГц.

и частоте Fx = 10 кГц, а также при напряжении источника управляющего сигнала (канал «Y») Uy = 200 мВ с частотой Fy = 1 МГц.

Рис. 6.29. Осциллограмма выходного сигнала схемы УУ рис. 6.28

На рис. 6.30 показана спектрограмма выходного сигнала УУ рис. 6.28 при напряжениях канала «Х»  , Fx = 10 кГц и напряжении канала «Y» Uy = 200 мВ, Fy = 1 МГц.

, Fx = 10 кГц и напряжении канала «Y» Uy = 200 мВ, Fy = 1 МГц.

Рис. 6.30. Спектрограмма выходного сигнала УУ рис. 6.28

Таким образом, предлагаемое техническое решение, являющееся альтернативным решением широко распространенного смесителя Гильберта, имеет функциональные преимущества по сравнению с классическим.